138

SEEDS/ISP3D is a federation of 130 re-

searchers form French electrical engi-

neering labs. The researchers share a

common but broad topic: integration of

power systems in 3D. Five other research-

er federations exist to work on the soci-

etal challenge of energy: this large group

is untitled SEEDS as for Electrical and

Power Electronic Systems in Societal Envi-

ronment (

).

Research areas

SEEDS/ISP3D group focus many areas re-

lated to integration of power systems. It

starts from materials for magnetic inte-

grated devices, high dielectric ceramics,

powders for alternative brazing of chips in

power module or special fluid for integrat-

ed active cooling. Integration of devices

deals with passive devices (capacitors, in-

ductance, transformer, super-cap, battery

cell), high-voltage wide band-gap devices

and high temperature SOI devices. Func-

tional integration is experimented on sili-

con up to double-face circuits. Efforts con-

cern alternative interconnection solutions

of chips in a 3D manner in a module.

Many results have been obtained on con-

verter architectures that benefit from 3D

integration like magnetically coupled poly-

phase converters. Converter architectures

are experimented to improve safety of ser-

vice and failure-mode operation.

Analyses of failure modes are carried out

on industrial and lab-scale modules to

feed research on lifetime prediction of

assemblies. Tests focus industrial applica-

tions in standard temperature range or

advanced power cores in extended tem-

perature range.

Innovative cooling approaches are pro-

posed within the semiconductor or at

package level. Passive cooling is ad-

dressed as well as active cooling based

on special fluids and motion schemes.

Wide bandgap devices are addressed

for high voltage applications and high-

er ambient temperature. SiC, GaN and

diamond are experimented and differ-

ent levels of integration are considered.

Power devices have been tested be-

tween -75°C to 300°C and more. Devel-

opment of dedicated drivers is hot topic.

CMOS SOI technology has been selected

and various driver test chips have already

been tested from -90°C to 300°C, mainly

in an attempt to exhibit failure modes

apart from functional verification.

Low-power monolithic integration re-

ceives a lot of attention and challeng-

ing system-on-chips have been demon-

strated.

INSA – Institut National des Sciences Appliquées Lyon

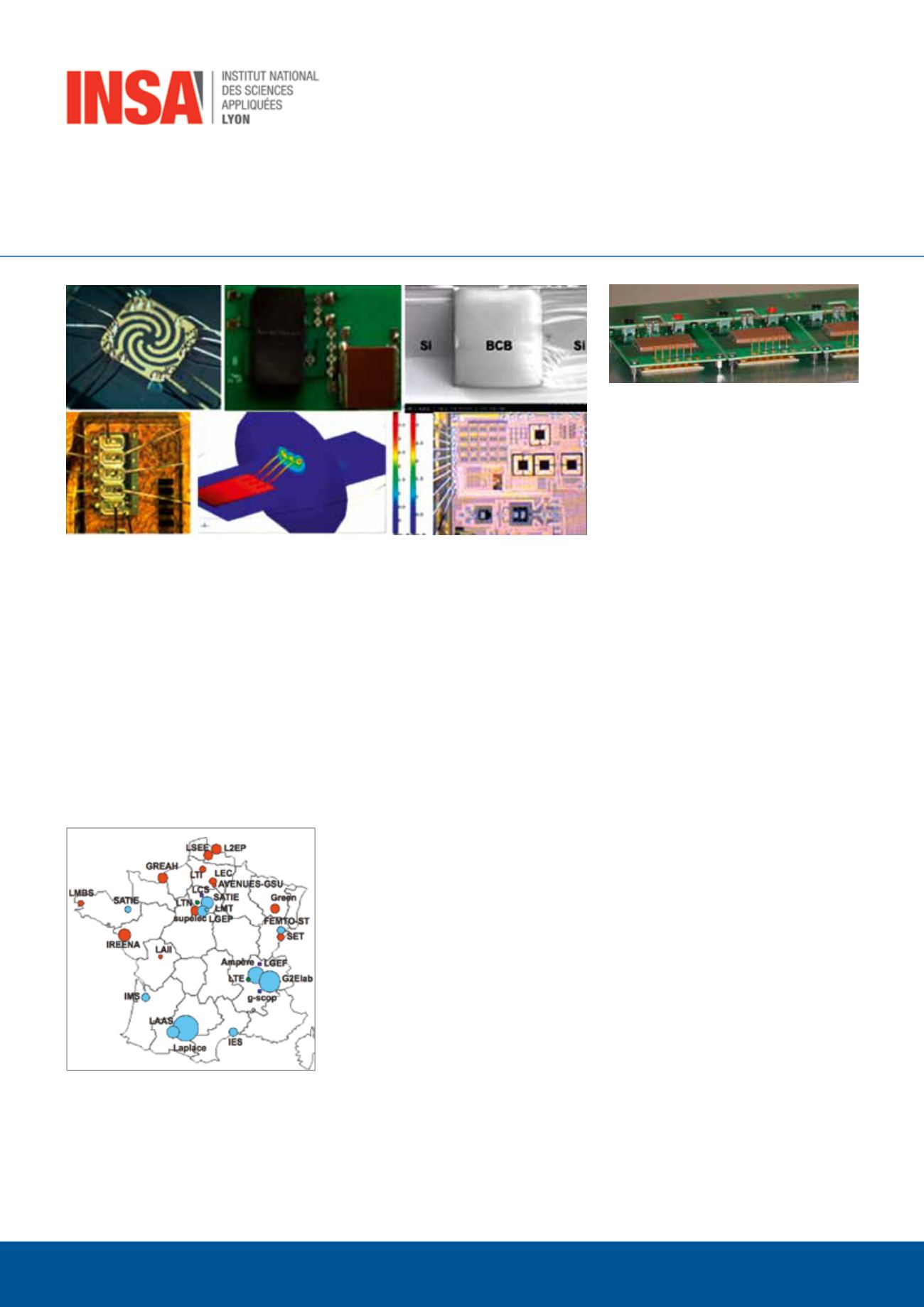

Top from right to left: SiC 6.5kV LTThysristor, integrated passive system, 3D super-capacitor cell. Bottom from

right to left: monolithic SiC converter, evaluation of EMC contribution, low power System-on-chip

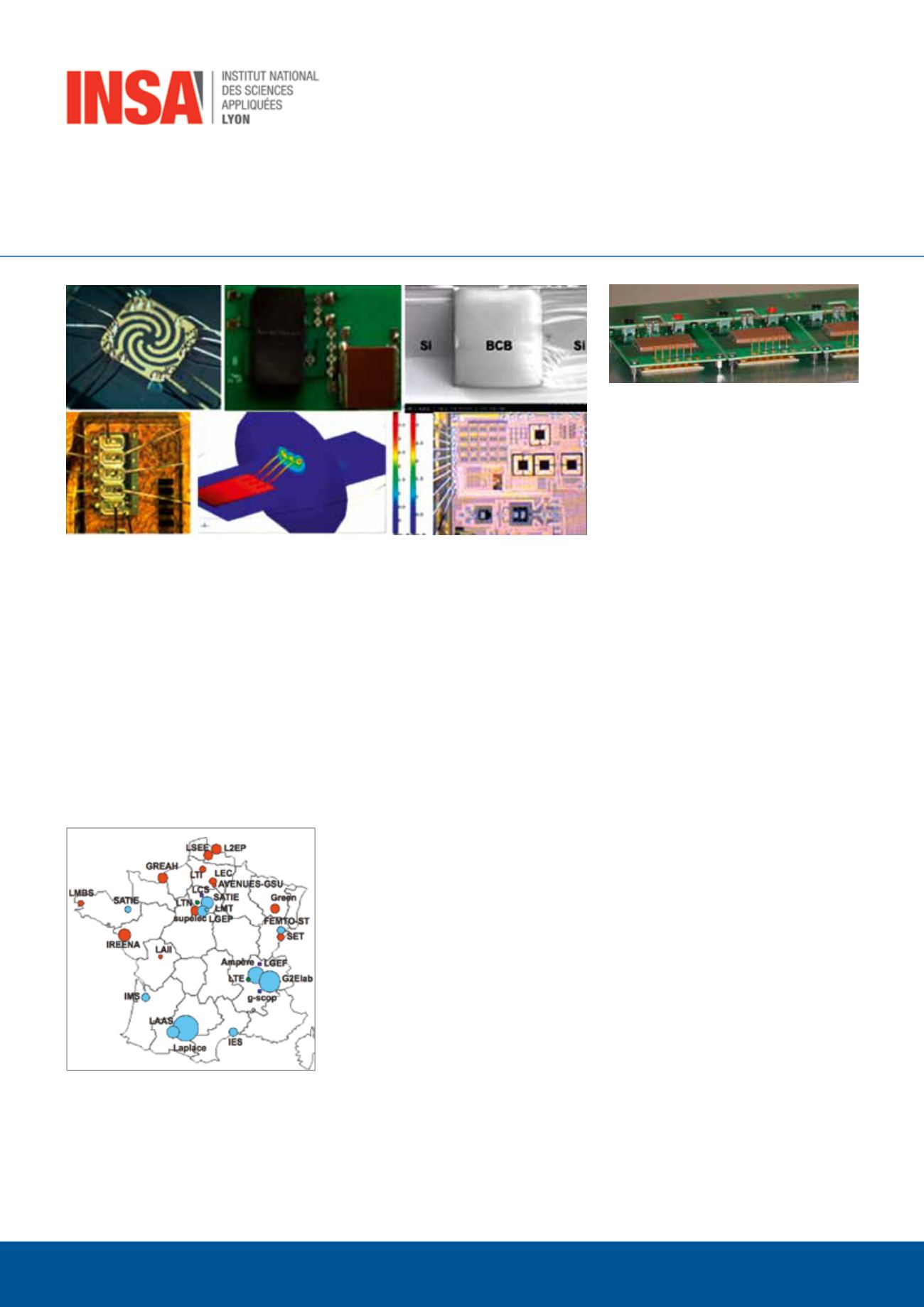

Map of labs involved in SEEDS/ISP3D group in France

SiC-JFET based inverter for 300°C ambient tempera-

ture operation