## **ECPE Guideline AQG 324**

# Qualification of Power Modules for Use in Power Electronics Converter Units in Motor Vehicles

Release no.: 03.1/2021

Release date: 31.05.2021

Contact: ECPE European Center for Power Electronics e.V.

Dipl.-Phys. Thomas Harder Landgrabenstrasse 94

90443 Nuremberg, Germany Email thomas.harder@ecpe.org Phone (+49) 911 8102 880

#### **Preface**

This Guideline was prepared by the ECPE Working Group 'Automotive Power Module Qualification' comprising ECPE member companies active in the automotive market. The original version is based on the supply specification LV 324 which has been developed by German automotive OEMs together with representatives from the power electronics supplier industry in a joint working group of ECPE and the German ZVEI association.

The industrial standards referenced in this document have consciously been selected in the specific versions or release years. This means they represent the technical state of the art of the industry, which was not prepared for automotive applications, but has been deemed suitable with regard to automotive applications. In particular, this avoids automotive-relevant details being omitted during revisions with a focus on non-automotive applications.

The official version of the Guideline released by the ECPE Working Group is a public document available on the ECPE web site (<a href="https://www.ecpe.org">www.ecpe.org</a>).

#### Legal disclaimer

No liability shall attach to ECPE e.V. or its directors, employees, member organizations or members of the responsible ECPE working group for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication of, use of, or reliance upon, this ECPE Guideline or any other ECPE publications.

ECPE guidelines and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action ECPE does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the ECPE guidelines or publications.

The ECPE Guideline AQG 324 is owned by ECPE European Center for Power Electronics e.V.

This ECPE Guideline AQG 324 is licensed under a Creative Commons license (license model CC BY ND) - with credit and sharing under the same conditions.

## **Contents**

| 1           | Scope                                                                            | 5        |

|-------------|----------------------------------------------------------------------------------|----------|

| 2           | Overview                                                                         | 7        |

| 3           | Referenced standards                                                             | 9        |

| 4           | Terms and definitions                                                            | 10       |

| 4.1         | Definitions                                                                      |          |

| 4.2         | Abbreviations - general                                                          | 12       |

| 4.3         | Abbreviations - electrical parameters                                            |          |

| 4.4         | Abbreviations - thermal parameters                                               |          |

| 4.5         | Abbreviations - humidity                                                         | 16       |

| 4.6         | Test times                                                                       |          |

| 4.7         | Standard tolerances                                                              |          |

| 4.8         | Standard values                                                                  |          |

| 5           | General part                                                                     | 18       |

| 5.1         | Prefequisites for crip usage in the module.                                      | 10       |

| 5.2         | Technology qualification                                                         | 18       |

| 5.3         | Qualification of special designs (of power el. modules) based on discrete device | _        |

| 5.4         | Sampling rates and measured value resolutions                                    |          |

| 5.5<br>5.6  | Design of insulation properties                                                  |          |

| 5.6<br>5.7  | Interface descriptionPhysical analysis                                           |          |

| 5. <i>1</i> | Procedure limitations                                                            |          |

| 6           |                                                                                  |          |

| <b>6</b> .1 | Module test QM – 01 Module test                                                  | 21       |

| 7           | Characterizing module testing                                                    |          |

| 7.1         | QC-01 Determining parasitic stray inductance (L <sub>p</sub> )                   |          |

| 7.2         | QC-02 Determining thermal resistance (R <sub>th</sub> value)                     |          |

| 7.3         | QC-03 Determining short-circuit capability                                       |          |

| 7.4         | QC-04 Insulation test                                                            |          |

| 7.5         | QC-05 Determining mechanical data                                                | 35       |

| 7.6         | Test sequence                                                                    |          |

| 8           | Environmental testing                                                            |          |

| 8.1         | Use of generic data                                                              | 37       |

| 8.2         | QE-01 Thermal shock test (TST)                                                   |          |

| 8.3         | QE-02 Contactability (CO)                                                        |          |

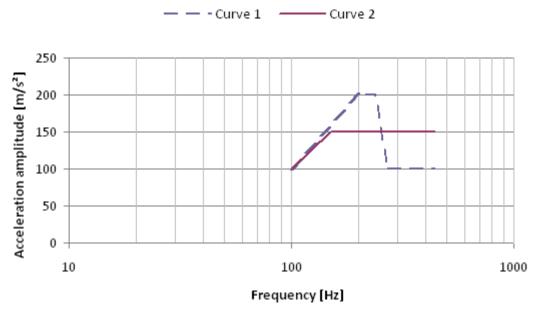

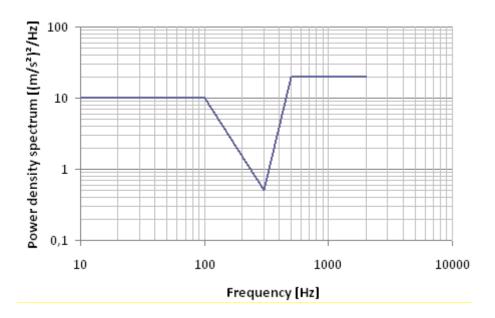

| 8.4         | QE-03 Vibration (V)                                                              | 40       |

| 8.5         | QE-04 Mechanical shock (MS)                                                      |          |

| 9           | Lifetime testing                                                                 |          |

| 9.1         | Use of generic data                                                              |          |

| 9.2         | QL-01 Power cycling (PC <sub>sec</sub> )                                         |          |

| 9.3<br>9.4  | QL-02 Power cycling (PC <sub>min</sub> )                                         |          |

| 9.4<br>9.5  | QL-03 High-temperature storage (HTS)                                             |          |

| 9.5<br>9.6  | QL-04 Low-temperature storage (LTS)  QL-05 High-temperature reverse bias (HTRB)  | 03<br>64 |

| 9.7         | QL-06 High-temperature gate bias (HTGB)                                          |          |

| 9.8         | QL-07 High-humidity, high-temperature reverse bias (H³TRB)                       | 69       |

|             |                                                                                  |          |

| Annex I     | Normative supplements                                      |

|-------------|------------------------------------------------------------|

| Annex I.A   | Test flow chart                                            |

| Annex I.B   | Delta qualification matrix                                 |

| Annex I.C   | Documentation of tests                                     |

|             |                                                            |

| Annex II    | Informative supplements                                    |

| Annex II.A  | Tracking of changes                                        |

| Annex II.B  | References                                                 |

| Annex II.C  | Typical aspects for physical analysis                      |

| Annex II.D  | <b>Guideline for Lifetime Calculation of Power Modules</b> |

|             |                                                            |

| Annex III   | Qualification of WBG-based power modules                   |

| Annex III.A | Qualification of SiC-based power modules                   |

# 1 Scope

#### **Preamble**

The AQG 324 represents an industry guideline based on best practices and outstanding requirement engineering alignment through the automotive supply chain for power electronic converter units. It also acts as blueprint for further approaches within the automotive transformation to overcome innovation blocking hurdles and to close gaps in product capability or corresponding assurance processes.

With the continuously increasing complexity of automotive electronics systems it is necessary to combine the expertise and to standardize approaches along the whole supply chain – different to outdated approaches where the alignment primarily occurred within a design hierarchical level, rather than from a complete system perspective.

Consequently, a core achievement has been and still is to define the same technical language as was only possible through jointly define and tune terms, definitions and processes.

This document defines requirements, test conditions and tests for validating properties, including the lifetime of power electronics modules and equivalent special designs based on discrete devices, for use in power electronics converter units (PCUs) of motor vehicles up to 3.5 t gross vehicle weight.

In case the power electronics components used in a PCU are not covered by the scope of this guideline, the supplier and the customer need to ensure, that the tests described in this document will be performed either in the qualification of the discrete devices, or on converter unit level. Should one or more of the tests described in AQG 324 guideline not be applicable in a certain design, the supplier must provide an explanation about the reason for the inapplicability to the customer.

The described tests concern the module design as well as the qualification of devices on module level (i.e. the assembly), but not the qualification of semiconductor chips or manufacturing processes.

These tests do not replace the qualification tests for complete vehicle PCUs.

The qualification requirements shall be extended or adapted, as necessary, on use of technologically novel designs.

The requirements, test conditions and tests listed in the main document essentially refer to power modules based on Si power semiconductors while the specialities of SiC-based power modules are addressed in Annex III.A of this guideline. Future releases of the AGQ 324 Guideline will address further wide bandgap power semiconductors (e.g. GaN), as well as novel assembly and interconnection technologies where other failure mechanisms become important compared to the todays technologies.

The tests listed in this document also apply for validating power module properties when using a thermal interface between the power module and the cooling system on PCU-level, if this interface is not a part of the module structure as a result of the design. Corresponding tests must be conducted on a reference test setup recommended and

documented by the module manufacturer, and any equivalent/generic test setups must be specified and documented.

#### Note:

If the thermal interface to the cooling system is implemented in the PCU and not in the power module, the module manufacturer cannot validate this interface. However, the module manufacturer must demonstrate that his module passes the module qualification in case of a connection as per the specification (recommended reference test setups). The PCU manufacturer must ensure that the thermal interface selected by it complies with the specifications from the module manufacturer.

#### Example:

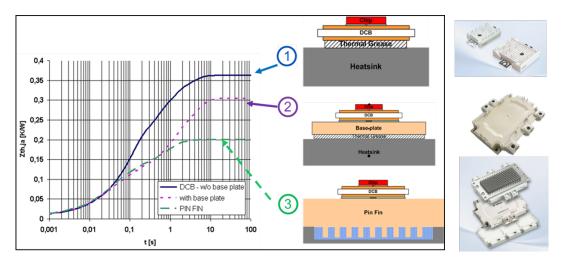

Validation of the thermal interface of power electronics modules, which are applied to a heat sink using a thermal interface material (TIM), is considered through specified reference test setups (including materials) in this document.

Validation of the thermal interface of power electronics modules with a pin-fin base plate located directly in the cooling medium is considered in this document.

Power electronics modules, which are already qualified or are currently being qualified according to AQG 324, are not affected by modified requirements defined in revisions of the AQG 324 that are released after the date of agreement of the qualification plan.

## 2 Overview

The tests described in the following serve to validate the properties and the lifetime of power electronics modules for use in the automotive industry.

The defined tests are based on the currently known failure mechanisms and the motor-vehicle specific usage profiles of power modules.

The validation takes place in the following steps:

#### QM – Module test

(Determines the electrical and mechanical parameters after the individual qualification tests)

- Gate parameters

- o Rated and leakage currents

- Forward voltages

- X-ray, scanning acoustic microscopy/tomography (SAM/SAT)

- Internal physical inspection/visual inspection (IPI/VI), optical microscope assessment (OMA)

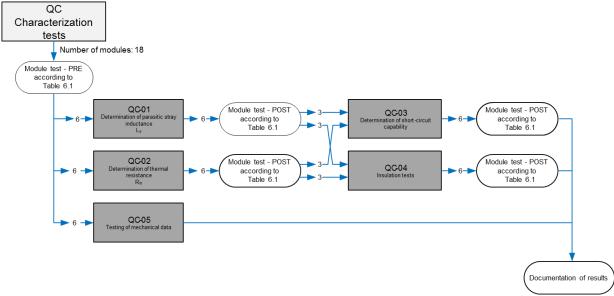

## • Characterizing module testing

- o QC-01 Determining parasitic stray inductance (Lp)

- o QC-02 Determining thermal resistance (Rth value)

- QC-03 Determining short-circuit capability

- o QC-04 Insulation test

- o QC-05 Determining mechanical data

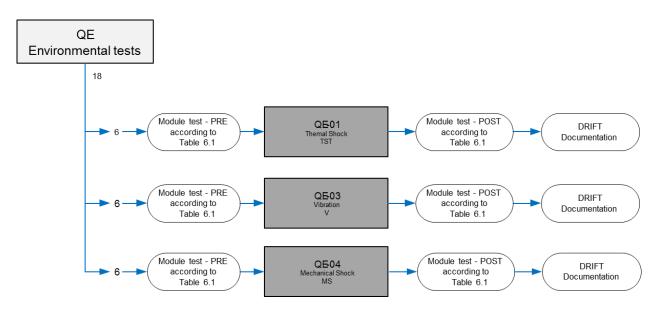

#### Environmental testing

- QE-01 Thermal shock test (TST)

- o QE-02 Contactability (CO)

- o QE-03 Vibration (V)

- QE-04 Mechanical shock (MS)

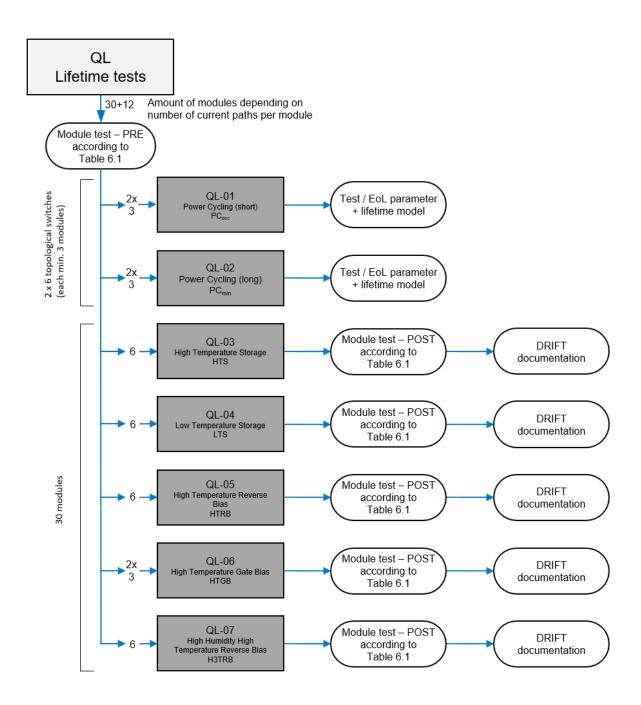

#### Lifetime testing

- QL-01 Power cycling (PCsec)

- o QL-02 Power cycling (PC<sub>min</sub>)

- QL-03 High-temperature storage (HTS)

- QL-04 Low-temperature storage (LTS)

- o QL-05 High-temperature reverse bias (HTRB)

- QL-06 High-temperature gate bias (HTGB)

- o QL-07 High-humidity high-temperature reverse bias (H<sup>3</sup>TRB)

#### Final testing for recording the electrical parameters of all DUTs

## Converting the test results into reliability data

Characterizing module tests serve to validate the fundamental electrical-functional properties and mechanical data of power modules. Among other things, these tests can provide early detection and evaluation of degradation-independent weak points in the

design (geometric arrangement, assembly and interconnection technology, semiconductor quality) which may gain further significance under degradation influence with regard to reliability and performance.

The environmental tests serve to verify the suitability of power electronics modules for use in motor vehicles. Physical analyses, verification of electrical and mechanical parameters, and insulation properties are used for the validation.

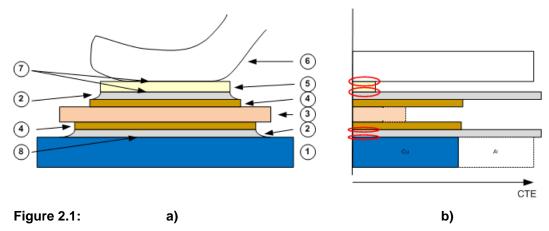

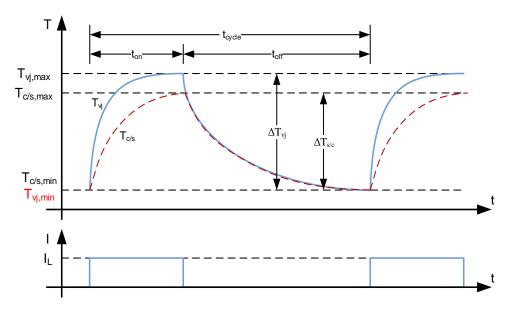

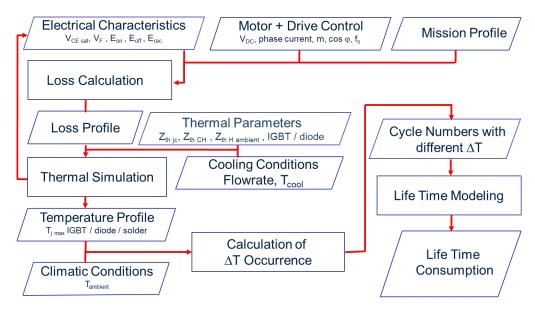

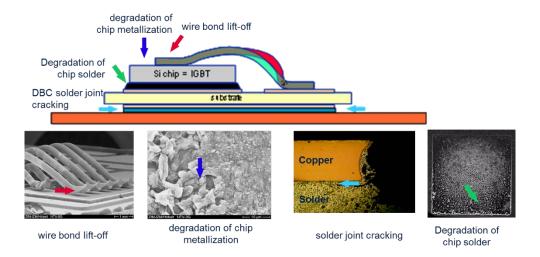

Lifetime testing has the objective of triggering the typical degradation mechanisms of power electronics modules. This process primarily differentiates between two failure mechanisms – fatigue of close-to-chip interconnections (chip-near) and fatigue of interconnections with a wider distance to the chip (chip-remote). Both failure mechanisms are triggered by thermomechanical stress between the different materials (with different thermal expansion coefficients) in each case (see Figure 2.1b).

The reliability of both, chip-near and chip-remote interconnections, depends on the thermal interface to the cooling system. For this reason, module qualification tests relating to these interconnections can only be tested using an application-based setup for modules without direct connection to the cooling system (connection, e.g. without base plate via TIM).

The number of devices under test (DUTs) for environmental and lifetime testing must be agreed upon between the PCU manufacturer and the module manufacturer in advance, following the test flow chart defined in Annex I.A. For special designs, this must be agreed upon.

- a) Sample cross section of a power electronics module

1: Base plate, 2: Solder, 3: Ceramic insulator (DCB, AMB), 4: Copper, 5: Chip,

6: Bonding wire, 7: Chip-near connection, 8: Chip-remote connection

- b) Schematic diagram of the thermal expansion coefficient in the individual layers of a power electronics module

# 3 Referenced standards

The following referenced documents are required for the use of this document. For references with a date, only the referenced issue is valid. For references without a date, the most recent issue of the referenced document (including all changes) is valid.

| Standard                     | Contents                                                                                                                                                                                                                                   |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISO/IEC 17025                | General Requirements for the Competence of Testing and Calibration Laboratories                                                                                                                                                            |

| IEC 60747-2:2016             | Semiconductor devices – Part 2: Discrete devices – Rectifier diodes                                                                                                                                                                        |

| IEC 60747-8:2010             | Semiconductor devices – Discrete devices – Part 8: Field-effect transistors                                                                                                                                                                |

| IEC 60747-9:2007             | Semiconductor devices – Discrete devices<br>Part 9: Insulated-gate bipolar transistors (IGBTs)                                                                                                                                             |

| IEC 60747-15:2010            | Semiconductor devices – Discrete devices Part 15: Isolated power semiconductor devices                                                                                                                                                     |

| IEC 60749-5:2017             | Semiconductor devices – Mechanical and climatic test methods – Part 5: Steady-state temperature humidity bias life test                                                                                                                    |

| IEC 60749-6:2017             | Semiconductor devices – Mechanical and climatic test methods – Part 6: Storage at high temperature                                                                                                                                         |

| IEC 60749-23:2011            | Semiconductor devices – Mechanical and climatic test methods – Part 23: High temperature operating life                                                                                                                                    |

| IEC 60749-25:2003            | Semiconductor devices – Mechanical and climatic test methods – Part 25: Temperature cycling                                                                                                                                                |

| IEC 60749-34:2010            | Semiconductor devices – Mechanical and climatic test methods – Part 34: Power cycling                                                                                                                                                      |

| IEC 60068-2-6:2007           | Environmental testing – Part 2-6: Tests – Test Fc: Vibration (sinusoidal)                                                                                                                                                                  |

| IEC 60068-2-27:2008          | Environmental testing – Part 2-27: Tests – Test Ea and guidance: Shock                                                                                                                                                                     |

| IEC 60068-2-64:2008          | Environmental testing – Part 2-64: Tests – Test Fh: Vibration, broadband random and guidance                                                                                                                                               |

| IEC 60664-1:2007             | Insulation coordination for equipment within low-voltage systems – Part 1: Principles, requirements and tests                                                                                                                              |

| DIN EN 60664-1<br>Addendum 1 | Insulation coordination for equipment within low-voltage systems – Part 2-1: Application guide - Explanation of the application of the IEC 60664 series, dimensioning examples and dielectric testing (IEC/TR 60664-2-1:2011 + Cor. :2011) |

| IEC 60664-4:2005             | Insulation coordination for equipment within low-voltage systems – Part 4: Consideration of high-frequency voltage stress                                                                                                                  |

| JESD22-A104F:2020            | Temperature Cycling                                                                                                                                                                                                                        |

| JESD22-A119:2015             | Low Temperature Storage Life                                                                                                                                                                                                               |

## 4 Terms and definitions

#### 4.1 Definitions

#### 4.1.1 Power electronics converter unit

A Power Electronics Converter Unit (PCU) in motor vehicles describes the most general form of a power electronics converter in a car, including for example the traction inverter, the LV and HV DC/DC converter, the on-board charger or the power electronics for electric power steering.

#### 4.1.2 Power electronics modules

More than one topological switch, e.g. insulated-gate bipolar transistors (IGBTs), metaloxide semiconductor field-effect transistors (MOSFETs) or diodes as well as possibly additional passive components (e.g. temperature sensors, capacitors), with one or several current paths integrated on or in a circuit carrier (e.g. substrate, PCB) form a power electronics module. All framed packages are considered to be modules.

## 4.1.3 Topological switch

A single semiconductor switch or several semiconductor switches connected in parallel which are controlled simultaneously to represent the function of a single switch.

Example: A half bridge consists of two topological switches – one high-side switch (HS) and one low-side switch (LS), whereby each topological switch can consist of one or several semiconductor switches/diodes connected in parallel.

### 4.1.4 Special designs based on discrete components

The control electronics on printed-circuit-boards (PCBs) installed in different PCUs, which contain circuit topologies with at least one topological switch consisting of discrete packaged IGBTs or MOSFETs, are considered power electronics modules as per section 4.1.2. If a driver infrastructure is additionally integrated in the board, the board represents an intelligent power module (IPM).

Note: One example for a special design is a B6 bridge (possibly including a driver) for controlling auxiliary power units on a FR4 PCB.

#### 4.1.5 Current path of a power electronics module

The current path of a power electronics module consists of one or several topological switches which are interconnected in different circuit topologies, depending on the function represented.

#### Note:

Half bridge, consisting of one high-side switch (HS) and one low-side switch (LS) with center tapping (phase tapping). Any other topologies are also conceivable. For topologies other than bridge circuits, the definition of the current paths has to be agreed advance.

## 4.1.6 Chip-near interconnection technology

The chip-near interconnection technology describes a design of the chip top side connection as well as the chip backside connection with the substrate.

## Examples:

Chip top surface: bond wire, ribbon bond, copper clip, sinter technology, µ-via connect Chip backside: chip soldering, sinter technology, diffusion soldering

## 4.1.7 Chip-remote interconnection technology

The chip-remote interconnection technology describes a design of the connections which do not directly include the chip. For this, a differentiation must be made between electrical and thermal interfaces. As a result of the design, chip-remote interconnection technology can be electrical as well as thermal.

### Examples:

Electrical interfaces: Design of the contacting for the load and auxiliary contacts. Thermal interfaces: System soldering between substrate and base plate (modules with base plate) or interface between module and cooling system (modules without base plate).

Note: For modules without base plate, the interface between module and cooling system, which in this case must be considered differently, must be validated with suitable tests during the PCU testing.

Special designs:

Chip-remote interconnection technology related to discrete package types integrated on a PCB (e.g. TO-247 housing): Interface between TO rear side and PCB or heat sink, e.g. with a heat conducting film.

#### 4.1.8 Circuit carrier

A circuit carrier is an unassembled or assembled wiring carrier for electronics.

#### 4.1.9 System

Functionally linked components e.g. a drive consisting of electric machine, power electronics, electronic control unit (ECU) and sensors form a system.

#### 4.1.10 Substrate

A substrate is a circuit carrier for power electronics components which can consist of different materials e.g. Al<sub>2</sub>O<sub>3</sub>, AlN, or organic-based materials e.g. in PCBs.

## 4.1.11 Direct and indirect cooling

In direct cooling the power module is part of the cooling system. Therefore, no thermal interface material (TIM) is used.

In indirect cooling the power module is assembled using TIM.

#### 4.1.12 Signal connections

Signal connections mean the control connections of power electronics modules.

## 4.1.13 High voltage (HV)

High voltage means voltages > 60 V for DC and voltages > 30 V for AC rms.

## 4.1.14 Reliability data

Specific to the IGBT, MOSFET, diode, bonds or soldering tests, this is the number of cycles for each DUT until the first end-of-life (EOL) criterion is reached in each case, taking into account identical failure criteria in each case in connection with the test parameters used.

## 4.2 Abbreviations - general

**Table 4.1: General abbreviations**

| AIT                         | Assembly and interconnection technology                                                                                                                                              |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMB                         | Active metal brazing                                                                                                                                                                 |

| CTE                         | Coefficient of thermal expansion                                                                                                                                                     |

| DCB                         | Direct copper bonded                                                                                                                                                                 |

| DoE                         | Design of experiments                                                                                                                                                                |

| DUT                         | Device under test                                                                                                                                                                    |

| EOL                         | End of life                                                                                                                                                                          |

| HTS                         | High-temperature storage                                                                                                                                                             |

| LTS                         | Low-temperature storage                                                                                                                                                              |

| HTRB                        | High-temperature reverse bias                                                                                                                                                        |

| HTGB                        | High-temperature gate bias                                                                                                                                                           |

| H <sup>3</sup> TRB          | High-humidity, high-temperature reverse bias                                                                                                                                         |

| Index " <sub>N</sub> "      | Nominal value – the nominal value of a quantity specified in the data sheet, e.g. voltage, current, resistance. In a power module, a value can be different for switches and diodes. |

| IPI/VI                      | Internal physical inspection/visual inspection                                                                                                                                       |

| IPM                         | Intelligent power electronics module                                                                                                                                                 |

| LSL                         | Lower specification limit                                                                                                                                                            |

| N <sub>f</sub>              | Number of cycles N until the first EOL criterion is reached in each case                                                                                                             |

| OMA                         | Optical microscope assessment                                                                                                                                                        |

| PC                          | Power cycling                                                                                                                                                                        |

| PC <sub>sec</sub> (seconds) | Power cycling with short load current on-time                                                                                                                                        |

| PC <sub>min</sub> (minute)  | Power cycling with longer load current on-time                                                                                                                                       |

| PCB                         | Printed circuit board                                                                                                                                                                |

| PCU                         | Power electronics converter unit                                                                                                                                                     |

| PPAP                        | Production part approval process                                                                                                                                                     |

| РТВ                         | Physikalisch Technische Bundesanstalt (German National Metrology Institute)                                                                                                          |

| SAM<br>SAT | Scanning acoustic microscopy Scanning acoustic tomography           |

|------------|---------------------------------------------------------------------|

| SOA        | Safe operating area                                                 |

| TCAD       | Technology computer aided design                                    |

| TIM        | Thermal interface material (e.g. thermal grease, phase change film) |

| TST        | Temperature shock test                                              |

| USL        | Upper specification limit                                           |

# 4.3 Abbreviations - electrical parameters

Table 4.2: Abbreviations for voltages, currents, inductances, resistances

| Vce                        | IGBT   | Collector-emitter voltage                                                                                             |

|----------------------------|--------|-----------------------------------------------------------------------------------------------------------------------|

| V <sub>CE,sat</sub>        | IGBT   | Collector-emitter voltage (forward voltage) in saturation operation                                                   |

| V <sub>BR,CE</sub>         | IGBT   | Collector-emitter breakdown voltage                                                                                   |

| V <sub>CE,max</sub>        | IGBT   | Maximum collector-emitter voltage                                                                                     |

| $V_{GE}$                   | IGBT   | Gate-emitter voltage                                                                                                  |

| $V_{\text{GE},\text{max}}$ | IGBT   | Maximum gate-emitter voltage                                                                                          |

| $V_{\text{GE,min}}$        | IGBT   | Minimum gate-emitter voltage                                                                                          |

| $V_{\text{GE,th}}$         | IGBT   | Gate-emitter threshold voltage                                                                                        |

| Ic                         | IGBT   | Collector current                                                                                                     |

| Icr                        | IGBT   | Collector current in reverse operation                                                                                |

| I <sub>CN</sub>            | IGBT   | Nominal collector current or continuous DC collector current                                                          |

| I <sub>CE,max</sub>        | IGBT   | Maximum blocking current                                                                                              |

| Isc <sub>1</sub>           |        | Short-circuit current type 1                                                                                          |

| Isc2                       |        | Short-circuit current type 2                                                                                          |

| ICE,leak                   | IGBT   | Collector-emitter leakage current                                                                                     |

| IGE,leak                   | IGBT   | Gate-emitter leakage current                                                                                          |

| VDS                        | MOSFET | Drain-source voltage (forward voltage)                                                                                |

| $V_{\text{BR},\text{DS}}$  | MOSFET | Drain-source breakdown voltage                                                                                        |

| $V_{\text{DS},\text{max}}$ | MOSFET | Maximum drain-source voltage                                                                                          |

| $V_{F,SD}$                 | MOSFET | Forward voltage of the internal body diode (corresponds to the voltage of the drain-source path in reverse operation) |

| V <sub>GS</sub>            | MOSFET | Gate-source voltage                                                                                                   |

| V <sub>GS,max</sub>        | MOSFET | Maximum gate-source voltage                                                                                           |

| V <sub>GS,min</sub>        | MOSFET | Minimum gate-source voltage                                                                                           |

| $V_{GS,th}$                | MOSFET | Gate-source threshold voltage                                                                                         |

| ID                       | MOSFET | Drain current                                                                                                                        |

|--------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>DN</sub>          | MOSFET | Nominal drain current                                                                                                                |

| $I_{\text{DS,max}}$      | MOSFET | Maximum blocking current                                                                                                             |

| I <sub>DS,leak</sub>     | MOSFET | Drain-source leakage current                                                                                                         |

| I <sub>GS,leak</sub>     | MOSFET | Gate-source leakage current                                                                                                          |

| V <sub>gate</sub>        |        | Gate voltage, general, e.g. V <sub>GE</sub> , V <sub>GS</sub>                                                                        |

| VR                       | diode  | Reverse voltage                                                                                                                      |

| $V_{\text{R,max}}$       | diode  | Maximum reverse voltage                                                                                                              |

| $V_{\text{BR},\text{R}}$ | diode  | Breakdown voltage                                                                                                                    |

| VF                       | diode  | Forward voltage                                                                                                                      |

| lF                       | diode  | Forward current                                                                                                                      |

| I <sub>R,max</sub>       | diode  | Maximum blocking current                                                                                                             |

| I <sub>R,leak</sub>      | diode  | Diode leakage current with reverse voltage applied                                                                                   |

| V <sub>test</sub>        |        | Test voltage, general, e.g. for insulation measurement                                                                               |

| IL                       |        | Load current, general                                                                                                                |

|                          |        | e.g. on the phase tapping of a current path to load a semiconductor element, to generate the power loss $P_{\text{V}}$               |

| V <sub>int.c</sub>       |        | Voltage in the intermediate circuit (DC link)                                                                                        |

| Lp                       |        | Parasitic stray inductance (or leakage inductance)                                                                                   |

| Ri                       |        | Internal resistance (e.g. of a voltage source in the test setup)                                                                     |

| PL                       |        | Power loss (e.g. $P_L = I_C \cdot V_{CE,sat}$ for IGBT, $P_L = I^2 \cdot R_{DS,on}$ for MOSFETs or $P_L = I_F \cdot V_F$ for diodes) |

All voltages and currents stated refer to the load or signal connections and generally do not include any voltage drops caused by the cables of the test setup.

Deviations from this, particularly for sources with internal resistance R<sub>i</sub> or for test setups with series resistors, must be stated for the respective test.

# 4.4 Abbreviations - thermal parameters

Table 4.3: Abbreviations for temperatures and cooling parameters

| T <sub>RT</sub>         | Room temperature                                                                |

|-------------------------|---------------------------------------------------------------------------------|

| T <sub>max</sub>        | Maximum specified operating temperature (data sheet information for the module) |

| T <sub>test</sub>       | Test temperature, general                                                       |

| ΔΤ                      | Temperature rise or deviation, general                                          |

| T <sub>cool</sub>       | Coolant temperature                                                             |

| T <sub>cool,min</sub>   | Minimum coolant temperature                                                     |

| T <sub>cool,max</sub>   | Maximum coolant temperature                                                     |

| T <sub>cool,in</sub>    | Temperature of cooling medium, inlet                                            |

| T <sub>cool,out</sub>   | Temperature of cooling medium, outlet                                           |

| Th                      | Temperature of the heat sink attached to the module                             |

| $\DeltaT_h$             | Temperature rise of the heat sink attached to the module                        |

| Tc                      | Temperature of the base plate on modules with base plate                        |

| ΔTc                     | Temperature rise of the base plate                                              |

| $\Delta T_{P,loss}$     | Temperature rise due to power losses                                            |

| Ts                      | Temperature of the sink on modules without base plate                           |

| ΔTs                     | Temperature rise of the sink on modules without base plate                      |

| T <sub>c/s</sub>        | Temperature of the generalized contact surface "c" or "s"                       |

| $\Delta T_{\text{c/s}}$ | Temperature rise of the generalized contact surface "c" or "s"                  |

| T <sub>vj</sub>         | Virtual junction temperature, general <sup>a</sup>                              |

| T <sub>vj,min</sub>     | Minimum virtual junction temperature <sup>a</sup>                               |

| T <sub>vj,avg</sub>     | Average virtual junction temperature <sup>a</sup>                               |

| T <sub>vj,max</sub>     | Maximum virtual junction temperature <sup>a</sup>                               |

| $\Delta T_{vj}$         | Temperature rise or deviation of the virtual junction temperature <sup>a</sup>  |

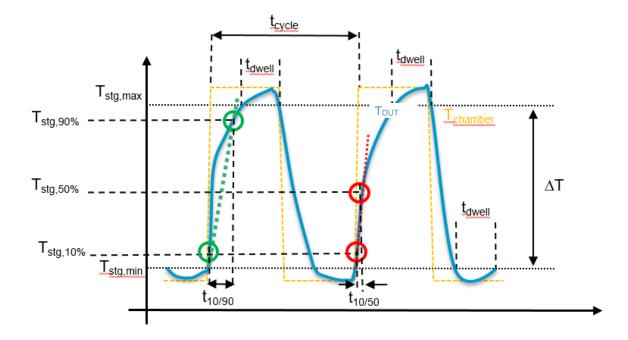

| T <sub>stg</sub>        | Storage temperature                                                             |

| T <sub>stg,min</sub>    | Minimum storage temperature                                                     |

| T <sub>stg,max</sub>    | Maximum storage temperature                                                     |

| Ta                      | Ambient temperature                                                             |

| Q <sub>cool</sub>       | Coolant flow rate (= $\Delta V_{cool} / \Delta t$ )                             |

| R <sub>th,j-c</sub>     | Thermal resistance of junction to case                                          |

| R <sub>th,j-s</sub>     | Thermal resistance of junction to sink                                          |

| R <sub>th,j-a</sub>     | Thermal resistance of junction to ambient                                       |

| R <sub>th,j-f</sub>     | Thermal resistance of junction to fluid                                         |

<sup>a</sup> Note: The junction temperature of a power semiconductor usually cannot be measured directly, but is indirectly concluded from a voltage measurement (e.g.  $V_{CE,sat}$  for IGBTs,  $V_{F,SD}$  of the internal body diode for MOSFETs, and  $V_F$  for diodes) (also see section Annex II.B [2]). Therefore,  $T_{vj}$  as the virtual junction temperature is stated instead of the real junction temperature  $T_j$ .

## 4.5 Abbreviations - humidity

Table 4.4: Abbreviations for humidity

| RH | Relative humidity |

|----|-------------------|

|----|-------------------|

## 4.6 Test times

Table 4.5: Abbreviations for test times

| ton               | On-time of a load (e.g. heating phase)        |

|-------------------|-----------------------------------------------|

| toff              | Off-time of a load (e.g. cooling phase)       |

| t <sub>r</sub>    | Rise time (e.g. from 10% to 90% gate voltage) |

| t <sub>f</sub>    | Fall time (e.g. from 90% to 10% gate voltage) |

| t <sub>test</sub> | Test duration                                 |

| tchange           | Transfer duration                             |

| tdwell            | Dwell time                                    |

#### 4.7 Standard tolerances

Tolerances refer to the measured value. For this, it must be ensured that the stated tolerances are adhered to independent of the tolerances of the testing system. If no other tolerances are stated in the individual tests, the tolerances from Table 4.6 must be used. When two tolerance values are stated, the first value indicates the upper tolerance and the second value indicates the lower tolerance of the value range.

**Table 4.6: Definitions of standard tolerances**

| Frequencies                        | ± 1%       |

|------------------------------------|------------|

| Measured temperatures              | ±2°C       |

| Indirectly determined temperatures | ±5°C       |

| Humidity                           | ± 5%       |

| Times                              | + 5%; - 0% |

| Voltages                           | ± 2%       |

| Currents                           | ± 2%       |

## 4.8 Standard values

Unless otherwise specified, the standard values in Table 4.7 apply.

**Table 4.7: Definitions of standard values**

| Room temperature | T <sub>RT</sub> = 23 °C ± 5 °C    |

|------------------|-----------------------------------|

| Humidity         | RH = 25% to 75% relative humidity |

| Test temperature | $T_{test} = T_{RT}$               |

# 5 General part

## 5.1 Prerequisites for chip usage in the module

The grade of automotive maturity of the power semiconductor in use within the power module has to be shown by a chip technology qualification conducted in advance. A suitable qualification procedure which has to be revealed by the supplier and agreed with the customer has to be applied.

If additional process steps, which expand the semiconductor stack (e.g. chip post processing for double-sided contacting) are required for the chip assembly in the module, the robustness and suitability for use of this new design must be verified. The verification must be obtained through Design of Experiments (DoE) results, TCAD simulations and a review confirmation by the semiconductor manufacturer. The verification must be documented.

## 5.2 Technology qualification

Technology qualification refers to the complete execution of all tests described under sections 6 to 9 for a new range of power electronics modules. In the following cases, a technology qualification must always be executed in case of changes to already qualified modules:

#### Design change:

- Material or geometry change of the base plate

- Material or geometry change of the substrate

- Material or geometry change of the module casing

- Change to at least one contacting surface of the devices

- Use of another material for die-attach (chip bottom side connection) or system soldering

- Change of the interconnection technology for chips for the die-attach (e.g. sintering, soldering, diffusion soldering) or top contacting (e.g. wire bonding, ribbon bonding, Cu clip, sintering)

### Chip change:

Use of other semiconductors or semiconductor materials or other passive components from the same or a different manufacturer

All changes concerning the module and semiconductor design must be reported. Process-related changes must be documented. Appropriate validation measures must be taken and documented based on agreement between the module supplier and the customer. The delta qualification matrix shown in Annex I.B shall be used as a guideline for the agreement.

# 5.3 Qualification of special designs (of power electronics modules) based on discrete devices

A reduced test scope must be used for the qualification of special designs. Correspondingly assembled discrete housed semiconductor switches must be qualified as per AEC-Q101, integrated circuits (ICs) (e.g. driver ICs in housings) as per AEC-Q100, and passive components as per AEC-Q200. For the special designs, only the tests QC-01 (stray inductance), QC-02 (thermal resistance) and QC-03 (short-circuit capability) must be executed. With regard to QC-01, the differences in the different current paths must be marked as well as evaluated and documented with regard to their criticality for reliable operation of the discrete semiconductor switches via simulation and in consultation with the semiconductor manufacturer. Concerning QC-02, a thermal management concept has to be provided which verifies compliance with the semiconductor specifications for each operating point. This also applies to the dynamic case. If necessary, the measuring setup must be adapted accordingly. The requirements for short-circuit capability described in QC-03 must also be tested for the special designs. The tests must be carried out by the manufacturer of the assembly or by the integrator into the PCU.

## 5.4 Sampling rates and measured value resolutions

The sampling rate and bandwidth of the measuring system must be adapted to the respective test. All measured values must be recorded with all maximum values (peaks).

The resolution of the measured values must be adapted to the respective test. It must be ensured that occurring voltage peaks do not lead to an overflow or that they cannot be measured in the case of an insufficient resolution. Data reductions/abstractions (e.g. limit monitoring) must not suppress irregularities.

When recording the measurement values for lifetime testing, it must be ensured that the measurement values are recorded with sufficient granularity regarding the expected lifetime, in order to ensure meaningful and precise determination of the EOL.

## 5.5 Design of insulation properties

The design of the air gaps and creepage distances as well as the selection of the solid insulating materials and gels must be indicated as per IEC 60664 Parts 1 and 4.

The following must be provided as a minimum:

- Creepage distances including tolerance in the specified temperature range

- Air gaps including tolerance in the specified temperature range

- Solid insulating materials and gels as well as their properties in the specified temperature range and for long-term influence of temperature, humidity and mechanical pressure (e.g. molding compound damage through spring clamp)

- Selected voltage values of the respective design

- Selected test voltages and test periods of the respective design

- Protection against soiling and soiling category with regard to the target application in the vehicle

- Sections and tables from IEC 60664 used for the design

Simulation of the mechanical strength of insulation parts

#### Note:

For stating the insulation materials and gels, it is sufficient to provide the material composition. Detailed information about the manufacturer and the type designation is not required.

## 5.6 Interface description

All interfaces must be described completely with regard to their electrical and mechanical properties.

## 5.7 Physical analysis

The physical analysis is a detailed analysis which must be conducted after failure of a DUT or after completing all electric testing on an OK part.

The following procedure shall be used:

- 1. Execution and documentation of all non-destructive tests/analyses

- 2. Derivation or joint coordination of additional tests/analyses based on the results of the non-destructive tests/analyses

- 3. Execution and documentation all destructive tests/analyses

- 4. Archiving of specimen and damaged parts

Examples for test methods are provided in Annex II.C.

The change in the module compared to the as-new condition must be evaluated.

The results must be documented in the test record.

#### 5.8 Procedure limitations

The test laboratory must be organized and operated as per ISO/IEC 17025 or IATF 16949. All test equipment used for measuring must be calibrated as per ISO/IEC 17025 (or as specified or recommended by the supplier) and it must be possible to trace the equipment back to the PTB or an equivalent national or European standards laboratory. The testing devices, equipment, setups and test methods must not distort the behavior of the DUT. These must be documented in the test report together with the accuracies and the expiration date of the calibration.

## 6 Module test

#### 6.1 QM - 01 Module test

## 6.1.1 General information

The module test serves to characterize the electrical and mechanical properties of the DUTs before (to ensure that only flawless DUTs enter into the qualification tests) and after the individual test sequences. Its purpose is to provide insight into the characteristic parameters of the modules, which can vary due to production fluctuations and the stress applied during the individual tests. Unless stated otherwise, the individual test steps of the module tests must be carried out before and after each of the individual test branches as per the test flow chart plan in Annex I.A and Table 6.1. They must be documented and the deviations outside the specified tolerances must be shown.

The objective of the measurements and tests is:

- · To ensure the absence of failures in all DUTs.

- To ensure that all requirements are met.

- To verify the functional behavior and the accuracy of all functions.

The measurements and tests 6.1.2 to 6.1.8 must be conducted as a minimum during the module tests. For all these tests, a defined shutting down/starting up of the DUTs from/into the load condition must be ensured, especially before/after the (intermediate) measurements. The temperature shall only be regulated to the target temperature of the intermediate measurement after shutting off the module. After the intermediate measurement, first the module must be started up and then the temperature must be regulated.

Note on data sheet values: Typical parameter values without range or limit information are not permitted as suitable criteria in the framework of module tests. If the range or limit information is missing in the data sheet, the module manufacturer must supply these later on. The values and the note about a special definition must be documented.

#### 6.1.2 End-of-line test

All DUTs must be tested as per the standard end-of-line test. With regard to 100% traceability, the results of the end-of-line test must be documented.

## 6.1.3 Testing the interconnection layers

The quality of the interconnection layers (e.g. solder, diffusion solder, sintered interconnection) and possible degradation due to voids, delamination or crack formation must be recorded and documented. For this, an examination using scanning acoustic microscopy (SAM) is recommended.

# 6.1.4 Nominal collector current or continuous DC-collector current (IGBT – modules)

The nominal collector current I<sub>CN</sub> must be defined and documented as per one of the following definitions:

- a) Nominal collector current = constant direct current with  $R_{th,j-c}$  with  $T_{vj} \le T_{vj,max}$  or

- b) Nominal collector current = collector current with typ. VCE, sat with maximum Rth, j-c

Note: Data sheets usually state the implemented nominal chip current (e.g. 800 A). This generally does not correspond to the nominal module current as a function of the thermal resistance and the cooling connection (e.g. 550 A).

## 6.1.5 Gate-emitter (IGBT)/gate-source (MOSFET) threshold voltage

The gate-emitter or gate-source threshold voltage ( $V_{\text{GE,th}}$  or  $V_{\text{GS,th}}$ ) must be determined at RT and the maximum specified operating temperature, which must be derived from the maximum junction temperature. This threshold voltage must be compared to the data sheet values.

## 6.1.6 Gate-emitter (IGBT)/gate-source (MOSFET) leakage current

The gate-emitter or gate-source leakage current (I<sub>GE,leak</sub> or I<sub>GS,leak</sub>) must be determined at RT and the maximum specified operating temperature, which must be derived from the maximum junction temperature. This threshold voltage must be compared to the data sheet values.

# 6.1.7 Collector-emitter (IGBT)/drain-source (MOSFET) reverse leakage current

The collector-emitter or drain-source leakage current (Ice,leak or Ide,leak) must be determined at RT and the maximum specified operating temperature, which must be derived from the maximum junction temperature.

In case of IGBTs with freewheeling diode connected anti-parallel, the leakage current is the sum of the reverse leakage current of the IGBT and the leakage current of the diode.

## 6.1.8 Forward voltage V<sub>CE,sat</sub> (IGBT), V<sub>DS</sub> (MOSFET), V<sub>F</sub> (diodes)

The forward voltage (V<sub>CE,sat</sub>, V<sub>DS</sub>, V<sub>F</sub>) must be determined at RT and the maximum specified operating temperature, which must be derived from the maximum junction temperature. This forward voltage serves as the data basis for the subsequent lifetime testing. For this, the forward voltage must be determined in pulsed operation in order to keep self-heating as low as possible.

## 6.1.9 Breakdown voltage $V_{BR,CE}$ (IGBT), $V_{BR,DS}$ (MOSFET), $V_{BR,R}$ (diodes)

The breakdown voltage is not defined on module level. Therefore, it has to be clarified in advance whether the device is capable to withstand this measurement. Hereby, there is a high risk of destroying the device by measurement due to local overheating (technology dependent). If the device allows the measurement, the breakdown voltage should be evaluated at 90% of the maximum blocking current I<sub>CE,max</sub> (IGBT), I<sub>DS,max</sub> (MOSFET), I<sub>R,max</sub> (diode).

## 6.1.10 IPI/VI, OMA

Damage or changes to the module due to load stress (failure analysis during qualification – see section 5.5) must be recorded with the following analysis methods and documented:

OMA (Optical Microscope Assessment)

IPI/VI (Internal Physical Inspection / Visual Inspection)

The test flow chart as per Annex I.A must be observed for all tests. If a component-specific adaptation of the test sequence is necessary (e.g. qualification of derivatives), the test flow chart can be adapted in agreement with the component manufacturer, but this must be documented.

|                | Readouts <sup>e</sup> (1,2,3,4,)    | End of Line<br>Test <sup>c</sup> (acc. to<br>6.1.2-6.1.8) | SAM System<br>/ die attach | Correlation <sup>a</sup><br>V <sub>GE,th</sub> / V <sub>GS,th</sub> | Correlation <sup>a</sup> | Correlation <sup>a</sup> I <sub>CE,leak</sub> / I <sub>DS,leak</sub> | Correlation <sup>a</sup><br>V <sub>CE</sub> / V <sub>DS</sub> | I VE      | Correlation <sup>a</sup><br>R <sub>th</sub><br>(acc. to QC-02) |           | Dynamic Test <sup>d</sup><br>(Double Pulse) | Isolation<br>Test <sup>b</sup> | Optional<br>IPI/VI, OMA |

|----------------|-------------------------------------|-----------------------------------------------------------|----------------------------|---------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------|---------------------------------------------------------------|-----------|----------------------------------------------------------------|-----------|---------------------------------------------|--------------------------------|-------------------------|

| QC-01 QC-04    | 1: Start of test<br>2: End of test  | 1,2                                                       | 1                          | 1,2                                                                 | 1,2                      | 1,2                                                                  | 1,2                                                           | 1,2       |                                                                |           |                                             | 1,2                            | 1,2                     |

| QC-05          | 1: Start of test<br>2: End of test  | 1                                                         | 1,2                        |                                                                     |                          |                                                                      |                                                               |           |                                                                |           |                                             | 1,2                            | 1,2                     |

| QE-01 TST      | 1: 0c<br>2: 500c (opt.)<br>3: 1000c | 1,2,3                                                     | 2,3                        | 1,2,3                                                               | 1,2,3                    | 1,2,3                                                                | 1,2,3                                                         | 1,2,3     | 1,2,3                                                          | 1,2,3     | 1,2,3                                       | 1,2,3                          | 1,2,3                   |

| QE-03 V        | 1: Start of test<br>2: End of test  | 1,2                                                       |                            | 1,2                                                                 | 1,2                      | 1,2                                                                  | 1,2                                                           | 1,2       |                                                                | 1,2       | 1,2                                         | 1,2                            | 1,2                     |

| QE-04 MS       | 1: Start of test<br>2: End of test  | 1,2                                                       |                            | 1,2                                                                 | 1,2                      | 1,2                                                                  | 1,2                                                           | 1,2       |                                                                | 1,2       | 1,2                                         | 1,2                            | 1,2                     |

| QL-01 PCsec    | 1: 0c<br>2: End of life             | 1,2                                                       | 2                          | 1,2 (opt)                                                           | 1,2 (opt)                | 1,2 (opt)                                                            | 1,2 (opt)                                                     | 1,2 (opt) | 1,2 (opt)                                                      | 1,2 (opt) | 1,2 (opt)                                   | 1,2                            | 1,2                     |

| QL-02 PCmin    | 1: 0c<br>2: End of life             | 1,2                                                       | 2                          | 1,2 (opt)                                                           | 1,2 (opt)                | 1,2 (opt)                                                            | 1,2 (opt)                                                     | 1,2 (opt) | 1,2 (opt)                                                      | 1,2 (opt) | 1,2 (opt)                                   | 1,2                            | 1,2                     |

| QL-03 HTS      | 1: 0h<br>2: 1000h                   | 1,2                                                       | 2                          | 1,2                                                                 | 1,2                      | 1,2                                                                  | 1,2                                                           | 1,2       |                                                                | 1,2       | 1,2                                         | 1,2                            | 1,2                     |

| QL-04 LTS      | 1: 0h<br>2: 1000h                   | 1,2                                                       | 2                          | 1,2                                                                 | 1,2                      | 1,2                                                                  | 1,2                                                           | 1,2       |                                                                | 1,2       | 1,2                                         | 1,2                            | 1,2                     |

| QL-05 HTRB     | 1: 0h<br>2: 1000h                   | 1,2                                                       |                            | 1,2                                                                 | 1,2                      | 1,2                                                                  | 1,2                                                           | 1,2       |                                                                | 1,2       | 1,2                                         | 1,2                            | 1,2                     |

| QL-06 HTGB     | 1: 0h<br>2: 1000h                   | 1,2                                                       |                            | 1,2                                                                 | 1,2                      | 1,2                                                                  | 1,2                                                           | 1,2       |                                                                | 1,2       | 1,2                                         | 1,2                            | 1,2                     |

| QL-07 H³TRB    | 1: 0h<br>2: 1000h                   | 1,2                                                       |                            | 1-2                                                                 | 1,2                      | 1,2                                                                  | 1,2                                                           | 1,2       |                                                                | 1,2       | 1,2                                         | 1,2                            | 1,2                     |

| Master samples | 1: 0h                               | 1                                                         |                            |                                                                     |                          |                                                                      |                                                               |           |                                                                |           |                                             |                                |                         |

<sup>&</sup>lt;sup>a</sup> Correlation - for the correlations, the T<sub>RT</sub> measured values of the characteristic data at the specified measurement time are compared against the values of the initial measurement. The values used for the correlation shall be documented accordingly and maximum percentages of the anticipated deviations shall be specified.

Table 6.1: Test-dependent module tests

b ISO test - in the ISO test, the insulation capability of the module is tested in accordance with the final series production test specifications. c Defined startup or shutdown before/after exposure to stress shall be ensured according to the specifications in the chapter "Module test".

<sup>&</sup>lt;sup>d</sup> Should be performed according to IEC 60747-15 2012 chapter 5.3.2.

<sup>e</sup> Additional intermediate measurements are not recommended for qualification but during development.

# 7 Characterizing module testing

The module tests described in sections 7.1 to 7.5 shall be carried out once and supply application-relevant characteristic properties of the module.

Characterizing module tests are the basic prerequisite for conducting subsequent environmental and lifetime testing. The application of generic data for characterizing module tests is not permissible.

## 7.1 QC-01 Determining parasitic stray inductance (L<sub>p</sub>)

## 7.1.1 Purpose

This test determines the parasitic stray inductance L<sub>p</sub> of the main contacts of a single current path of the DUT.

#### 7.1.2 Test

The parasitic stray inductance L<sub>p</sub> must be determined as per IEC 60747-15:2012, section 5.3.2 (double pulse testing). If the DUT has several identical current paths, the maximum value of all current paths must be indicated for the parasitic stray inductance.

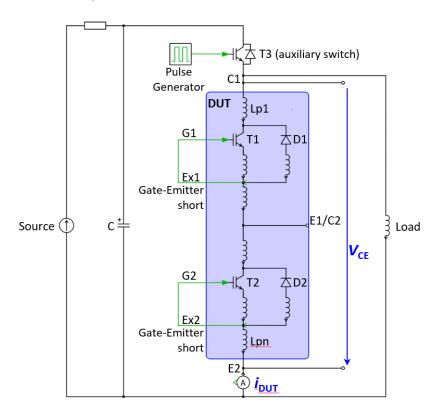

The measurement must be performed during the turn-off of the semiconductor T3 (auxiliary switch), see Figure 7.1.

The scope of random samples for this test must be taken from the test flow chart.

Figure 7.1: Test setup for stray inductance measurement

## 7.1.3 Requirement

The test conditions, the test setup and the test results (measured curves documented by the manufacturer to determine the parasitic stray inductance  $L_p$ ) must be provided to the purchaser.

#### Note:

The parasitic stray inductance of the power electronics module installed in the PCU can have a crucial quality-relevant impact on the function or reliability of the PCU, depending on the PCU structure.

## 7.2QC-02 Determining thermal resistance (Rth value)

## 7.2.1 Purpose

This test determines the thermal resistance of the individual devices on the power module.

#### 7.2.2 Test

The test must be conducted as per IEC 60747-15:2012, section 5.3.6, with the following additions:

IEC 60747-15:2012, section 5.3.6.1: thermal resistance R<sub>th,j-c</sub>

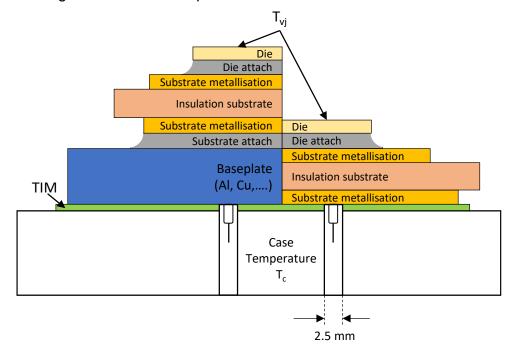

- The position and distances of the temperature sensor, which determine the reference point for determining the reference temperature T<sub>c</sub>, must be documented.

- The temperature sensor must be guided as closely as possible to the module (as per figure 7.2) to allow optimum determination of the reference point for determining the reference temperature T<sub>c</sub> for the case-related thermal resistance:

Figure 7.2: Reference point for determining the reference temperature Tc

The thermal resistance  $R_{\text{th,j-c}}$  must therefore be determined using the following formula:

$$R_{th,j-c} = \frac{T_{vj} - T_c}{P_v}$$

- For measuring T<sub>c</sub>, a hole must be made in the heat sink, centrally below the device under test (DUT). The hole must have a diameter of 2.5 mm, see Figure 7.2.

- When determining the thermal resistance R<sub>th,j-c</sub>, the type (manufacturer, designation, thickness, thermal conductance) of the TIM material used during the measurement must also be stated.

IEC 60747-15:2012, section 5.3.6.4: thermal resistance Rth,j-s

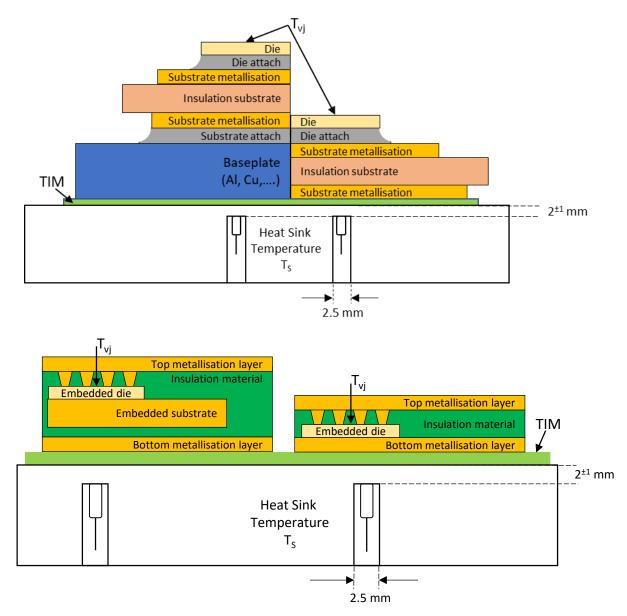

• Reference point for determining the reference temperature T<sub>s</sub> for the heat-sink-related thermal resistance:

Figure 7.3: Reference point for determining the reference temperature T<sub>s</sub>, for conventional (top) and embedded (bottom) power modules

The thermal resistance R<sub>th,j-s</sub> must therefore be determined using the following formula:

$$R_{th,j-s} = \frac{T_{vj} - T_s}{P_v}$$

- For measuring T<sub>s</sub>, a blind hole must be made in the heat sink, centrally below the DUT. The blind hole must have a diameter of 2.5 mm and end 2 ±1 mm below the heat sink surface, see Figure 7.3.

- When determining the thermal resistance R<sub>th,j-s</sub>, the type (manufacturer, designation, thickness, thermal conductance) of the TIM material used during the measurement must also be stated.

Supplementary tests for IEC 60747-15:2012:

• For power modules with direct contact to liquid cooling media, it is necessary to determine the thermal resistance between the junction temperature and the cooling medium (Rth,j-f).

For this, the coolant flow must be adjusted as per common applications and the coolant, (e.g. ethylene glycol water/propylene glycol water), the coolant circuit pressure and the coolant flow must be documented.

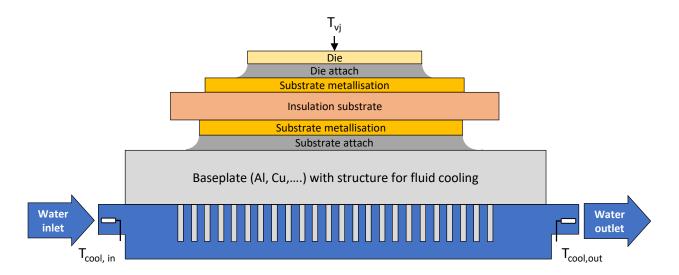

The reference points for determining the temperatures of the cooling medium ( $T_{cool,in}$ ,  $T_{cool,out}$ ) for the thermal resistance related to the coolant according to Figure 7.4:

Figure 7.4: Reference point for determining the reference temperature T<sub>COO</sub>I

• The thermal resistance Rth,j-a must therefore be determined using the following formula:

$$R_{th,j-a} = R_{th,j-f} = \frac{T_{vj} - \left(\frac{T_{cool,in} + T_{cool,out}}{2}\right)}{P_{v}}$$

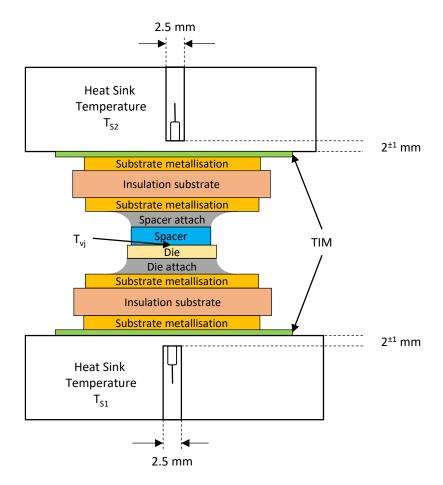

• For power modules with double sided cooling, the measurement must be performed with simultaneous cooling from both sides.

Two heat sink temperatures,  $T_{S1}$  and  $T_{S2}$ , must be measured. The sensors must be placed in blind holes on each side, centrally below the DUT. Each blind hole must have a diameter of 2.5 mm and end 2 ±1 mm below the heat sink surface, see Figure 7.5.

Figure 7.5: Reference points for determining the heat sink temperatures T<sub>S1</sub> and T<sub>S2</sub> for double sided cooling modules

The thermal resistance R<sub>th,j-s</sub> must therefore be determined using the following formula:

$$R_{th,j-s} = \frac{T_{vj} - \left(\frac{T_{S1} + T_{S2}}{2}\right)}{P_{v}}$$

Deviating cooling solutions and measurements shall be agreed between customer and supplier (e.g. measuring of the  $R_{th}$  from  $T_{vj}$  to liquid for non-direct water-cooled power modules).

The scope of random samples for this test must be taken from the test flow chart.

## 7.2.3 Requirement

The test conditions (with information about the reference point for the temperature on casing, heat sink or cooling medium) and the test results must be documented.

For power modules with several devices or current paths, it must be indicated how the devices were connected and/or operated for determining the thermal resistance.

## 7.3 QC-03 Determining short-circuit capability

### 7.3.1 Purpose

In the frame of this test, the short-circuit capability specified in the data sheet shall be verified. If the module has no short-circuit capability according to the manufacturer's specifications, this test is omitted. Omitting the test must be justified and documented in the test report.

The test is described by the voltages  $V_{CE}$  or  $V_{DS}$  and  $V_{GE}$  or  $V_{GS}$ , the short-circuit pulse duration  $t_p$  and the junction temperature  $T_{vj}$  at the time of the start of the short-circuit pulse duration.

#### 7.3.2 Test

For the short-circuit test it must be ensured that the semiconductor device is heated-up to the maximum virtual junction temperature at the start of the test.

A short circuit of type 1 as well as a short circuit of type 2 can be used for the test.

To maintain the voltages within the permissible range during the test, the DUT can be connected with a gate-emitter clamping or with a collector-gate clamping. It must be ensured beforehand that this causes no relevant heating up.

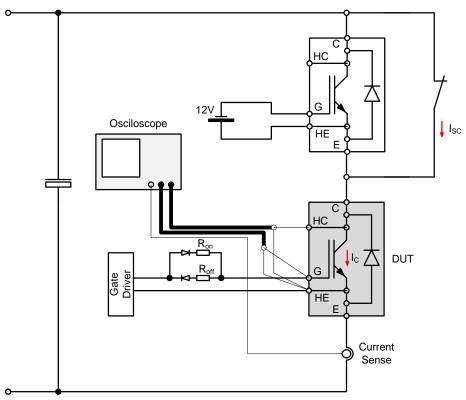

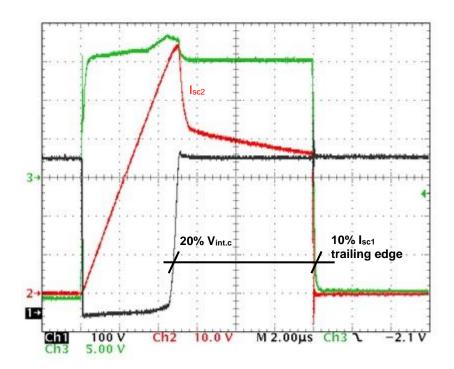

Figure 7.6: Test setup for short-circuit capability

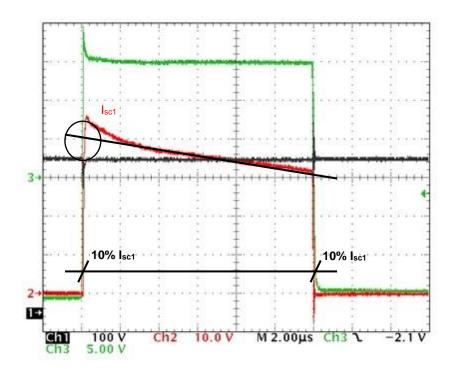

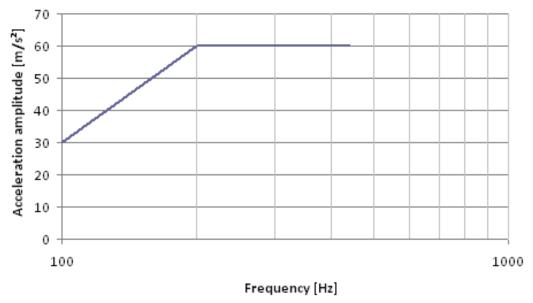

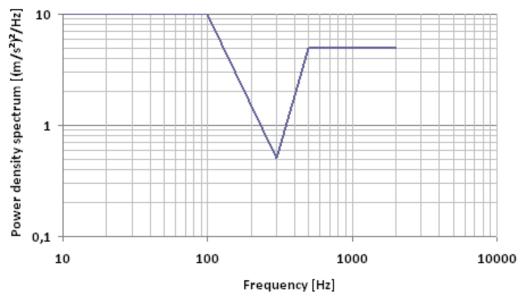

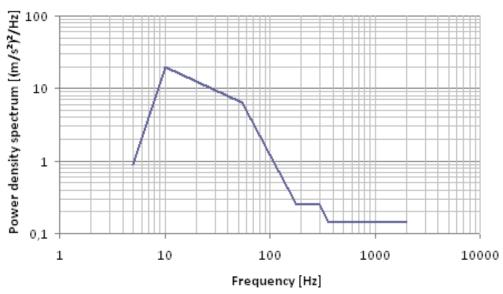

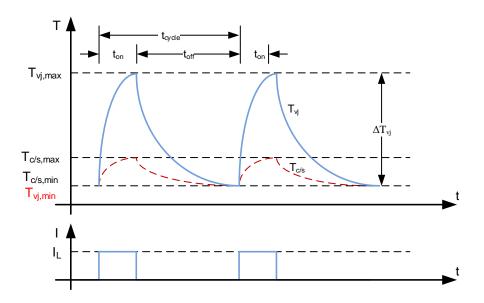

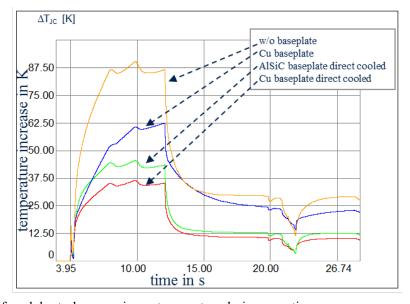

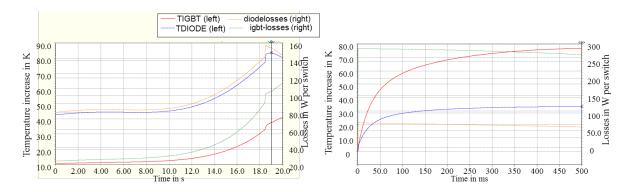

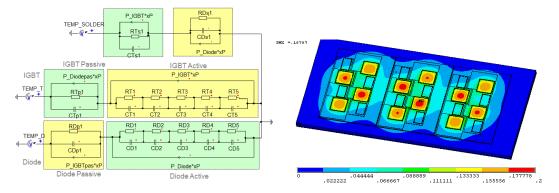

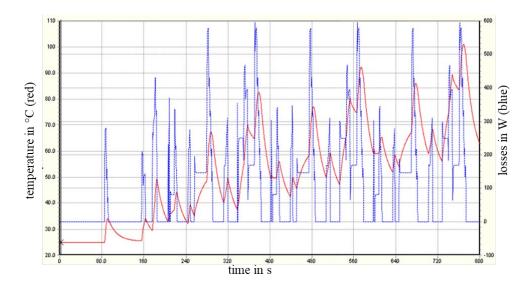

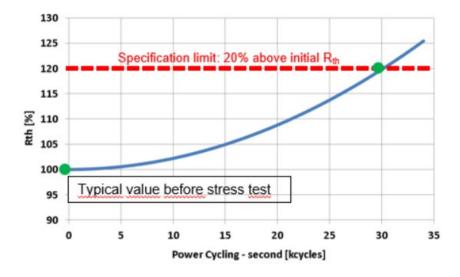

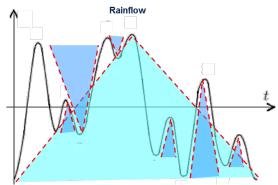

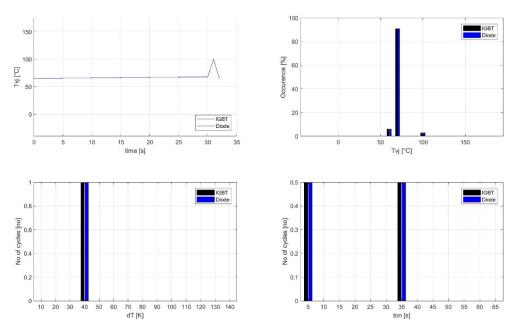

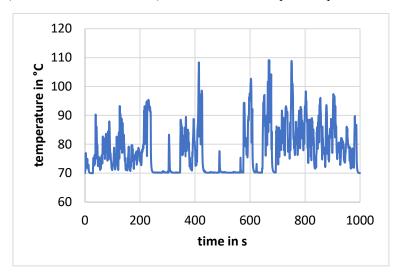

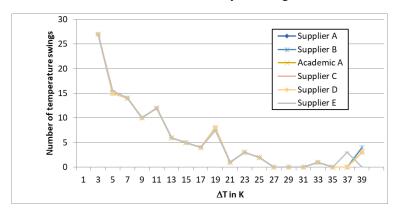

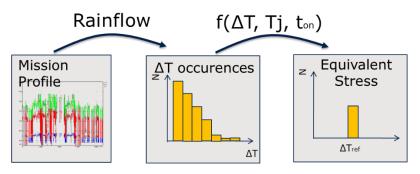

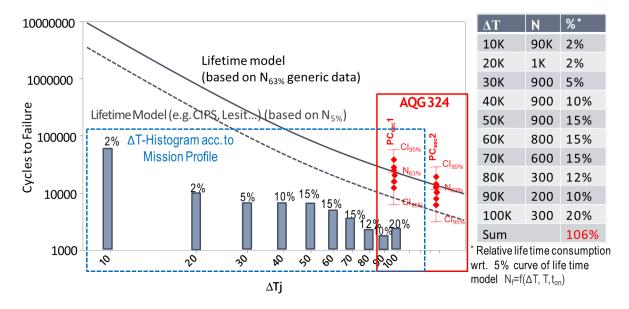

#### Short circuit type 1 (hard switch failure):